Publication trimestrielle du Laboratoire

d'analyse et d'architecture des systèmes du CNRS

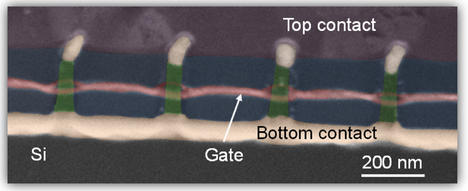

© G. Larrieu et X-L Han/LAAS-CNRS

La miniaturisation des composants électroniques n'a pas encore atteint ses limites. Deux chercheurs du LAAS et de l'IEMN viennent de construire un transistor de taille nanométrique au comportement exceptionnel pour un dispositif de cette dimension. Pour y parvenir, ils ont conçu une architecture originale en trois dimensions composée d’un réseau vertical de nanofils dont la conductivité est contrôlée par une grille de seulement 14 nm de longueur. Ces résultats offrent une alternative aux structures planes des microprocesseurs et des mémoires actuels. Ces transistors 3D permettraient ainsi d’accroître la puissance des dispositifs microélectroniques.

Les transistors, briques de base de la microélectronique, sont composés d’un élément semi-conducteur, dit canal, reliant deux bornes. Le passage du courant entre les bornes est contrôlé par une troisième borne appelée grille : c’est celle-ci qui, tel un interrupteur, détermine si le transistor est ouvert ou fermé. Au cours des 50 dernières années, la taille des transistors n’a cessé de se réduire, permettant la montée en puissance des appareils microélectroniques. Les architectures planes des transistors actuels limitent cependant leur miniaturisation. Au-delà d’une taille minimale, le contrôle du canal des transistors par la grille est moins efficace et l'on observe notamment des fuites de courant qui perturbent les opérations logiques réalisées par ces ensembles de transistors.

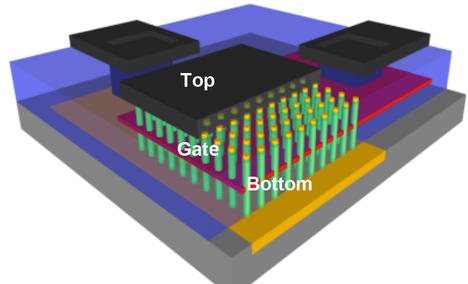

© X-L Han et G. Larrieu

Les deux chercheurs ont, pour la première fois, construit un transistor nanométrique véritablement en 3D, dont le niveau de commande transistor est très élevé pour un dispositif de cette dimension. Le transistor est constitué d’un réseau serré de nanofils verticaux d’environ 200 nm de longueur reliant deux plans conducteurs. Une grille de chrome entoure complètement chaque nanofil et contrôle le passage du courant. La longueur de la grille est de seulement 14 nm, contre 28 nm pour les transistors des puces actuelles. Néanmoins, sa capacité à contrôler le passage du courant dans le canal du transistor est compatible avec les besoins de la microélectronique actuelle.

Une telle architecture permettrait de construire des microprocesseurs faits d’un empilement de transistors. L’on pourrait ainsi augmenter leur nombre dans un espace donné, et, par conséquent, augmenter les performances des microprocesseurs ou la capacité des mémoires. Un autre atout important de ces composants est que leur fabrication est relativement simple et ne nécessite pas de procédés lithographiques[1] de haute résolution. Enfin, ils pourraient s’intégrer facilement aux éléments microélectroniques classiques utilisés actuellement par l’industrie.

Un brevet a été déposé. Les efforts vont maintenant porter sur la taille de la grille qui pourrait être inférieure à 10 nm tout en offrant encore un contrôle du transistor satisfaisant, après quoi pourrait commencer, de concert avec des industriels, la conception des dispositifs électroniques futurs qui mettront à profit l’architecture 3D de ces transistors.

Ces travaux ont été publiés dans la revue Nanoscale (Vertical nanowire array-based field effect transistors for ultimate scaling. G. Larrieu and X.-L. Han) et diffusés plus largement par le CNRS dans un communiqué de presse.

[1] Un procédé lithographique est une technique largement utilisée en micro/nano technologie pour réaliser des texturations de surface par transfert de motifs définis dans une résine sensible.