## **Building confidence in SiC and GaN technologies: PROOF's role in IRT collaborative projects**

WS – PROOF 30.04.2024

Fabio Coccetti IRT Saint Exupéry (Toulouse)

fabio.coccetti@irt-saintexupery.com

www.irt-saintexupery.com

## **CONTEXT & MOTIVATION**

The main vector to enable energy transition is ELECTRIFICATION of systems and functions!

Main challenges

Function Densification

→ Densification KW/Liter - KW/Kg

→ Efficiency (reducing losses) > 95%

- Wide Band Gap Power Electronics !

- High Voltage (current) !

- Functional Safety (Dependability)

**Safety - Reliability – Availability – Maintainability** – (Testability - Reparability – Confidentiality – Integrity – Certificability)

-> CONFIDENCE in the underlying technology !

by 2 main levers

french INSTITUTES OF TECHNOLOGY

р

а g

e

4

5/22/2024

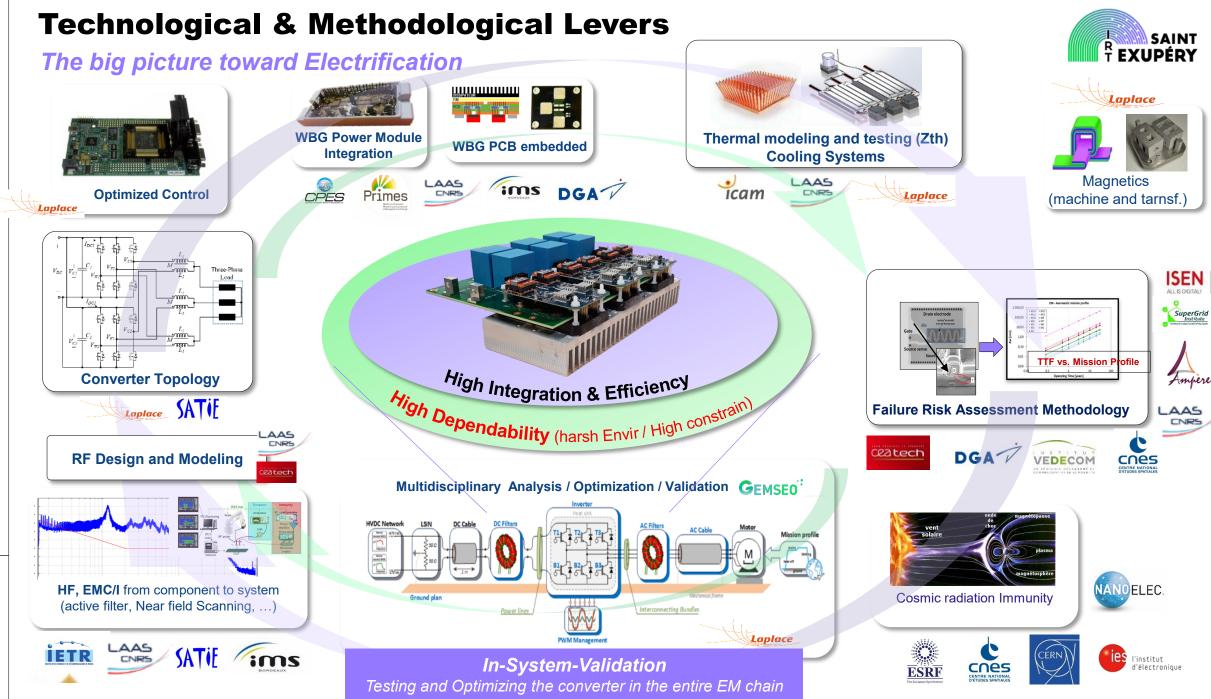

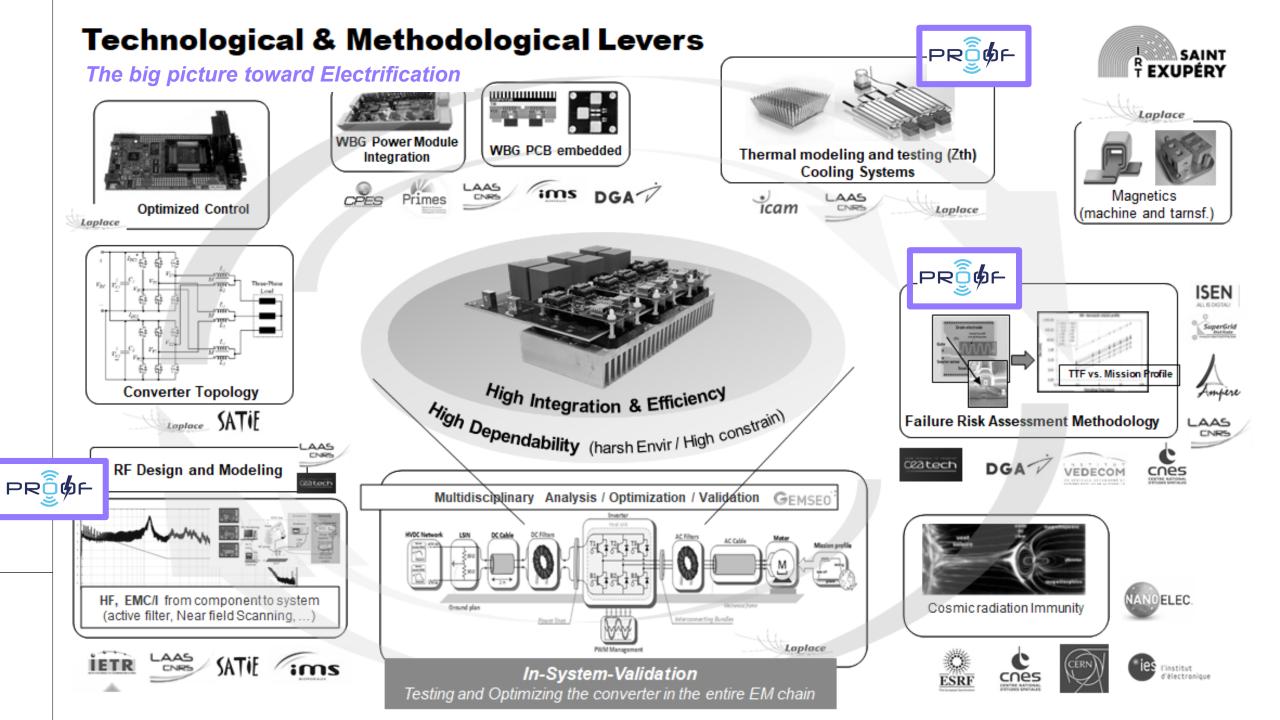

## **Technological & Methodological Levers**

The big picture

## Performance **DENSIFICATION** !

Power density, efficiency, ....

# **CONFIDENCE** in Design and Use !

Margin Aware Design and Use RULES!

## EXPLICABLE !

Provide the underlying Physics (of Failure, of working)

р а

> g e

5

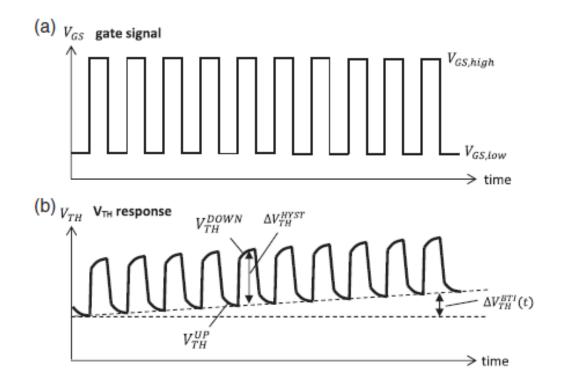

## **Need of reliability insight**

at semiconductor (die) level

T. Aichinger, et al., Microelectronics Reliability 80 (2018) 68-78.

## How to discriminate between reversible (recovery) and not reversible phenomena (aging) !!

Tt FRENCH INSTITUTES OF TECHNOLOGY

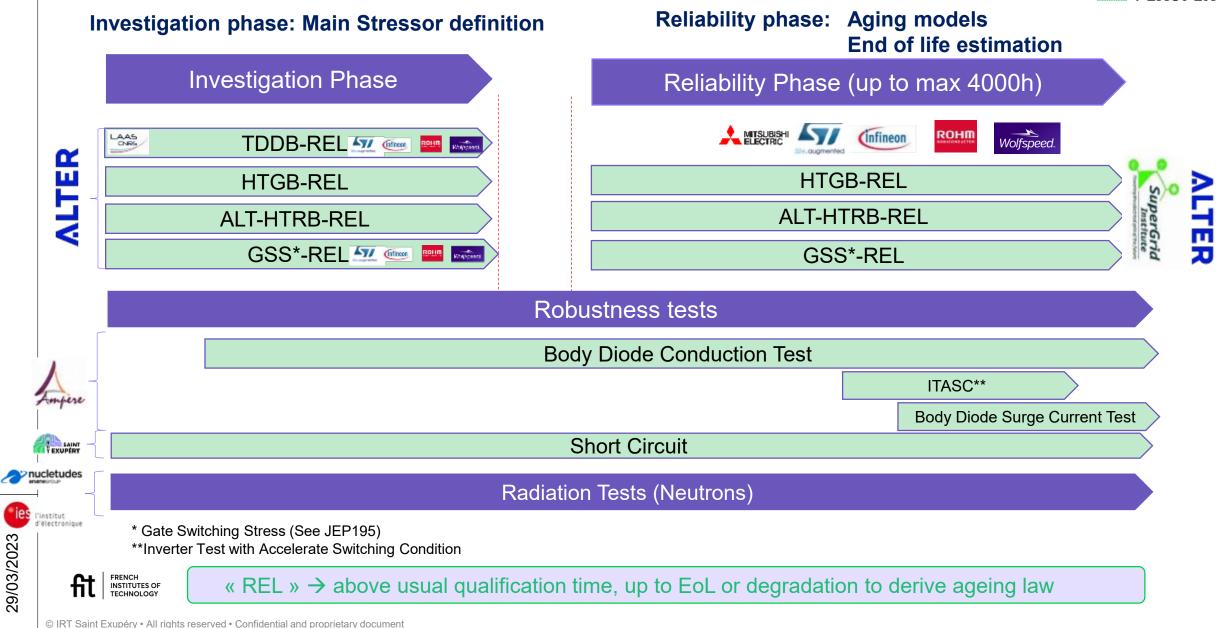

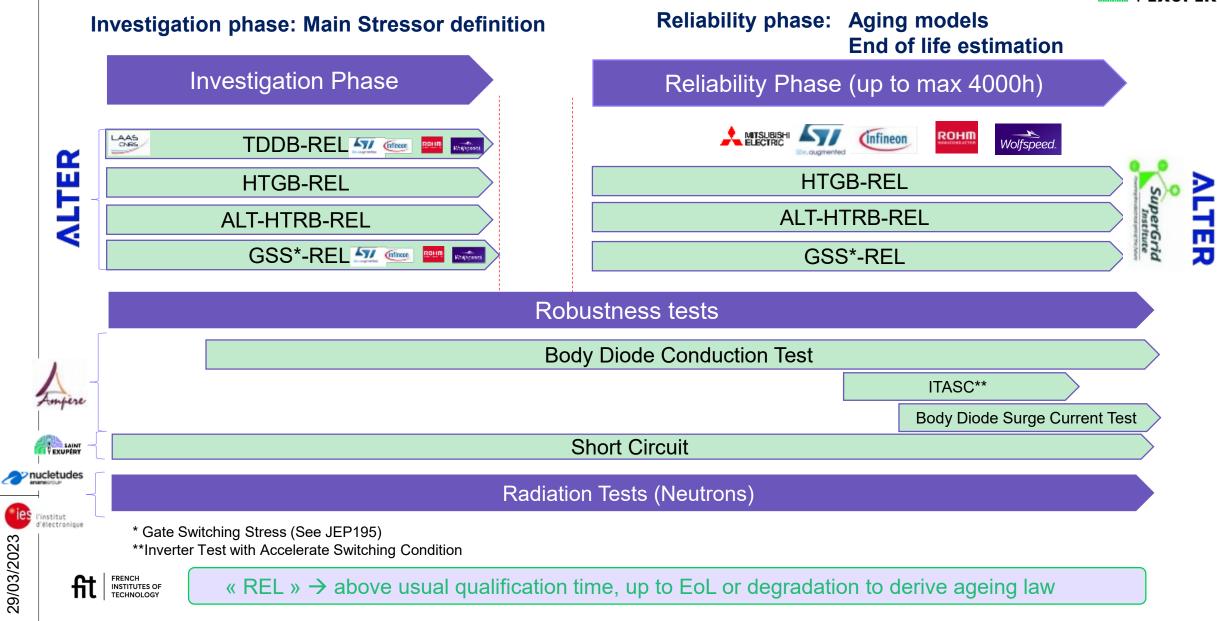

## **Reliability Methodology**

7

Optimal Approach toward costs-effective test of SiC MOSFET

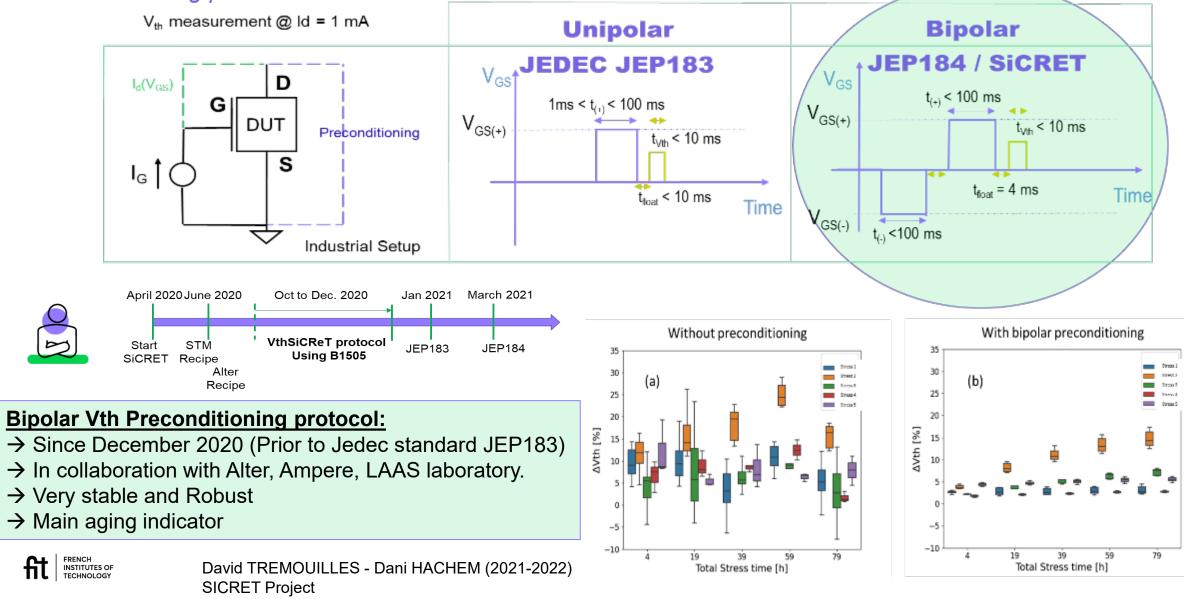

## **Vth Characterization for SiC MOSFET**

Preconditioning protocol definitions

8

© IRT Saint Exupéry • All rights reserved • Confidential and proprietary document

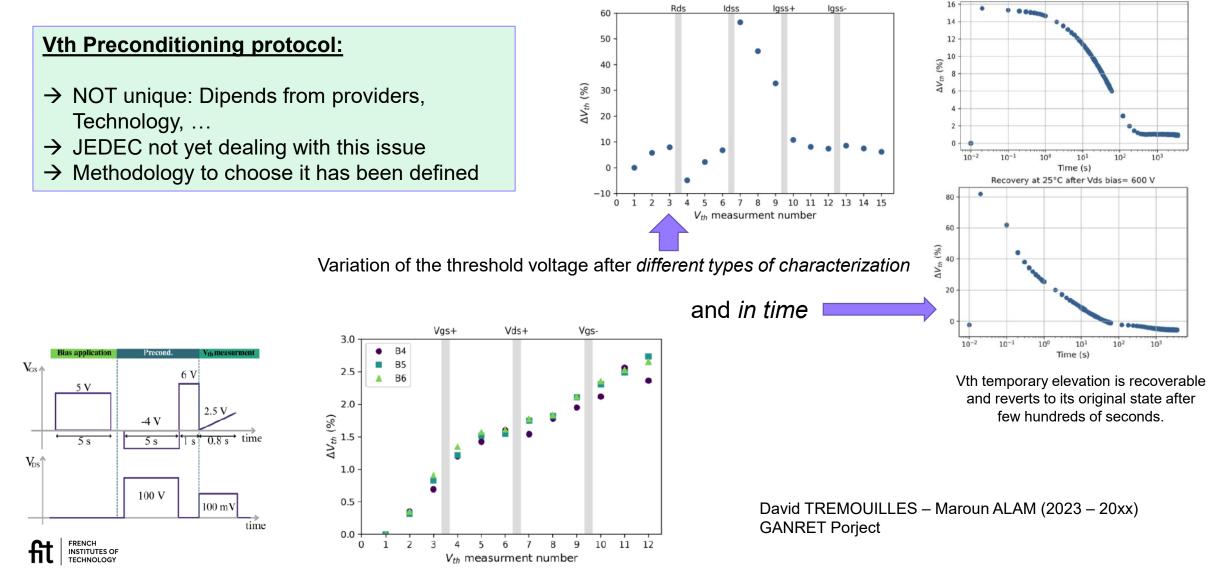

## **Vth Characterization for Power GaN HEMT**

Recovery at 25°C after Vgs bias= 4 V

Preconditioning protocol definitions

9

29/03/2023

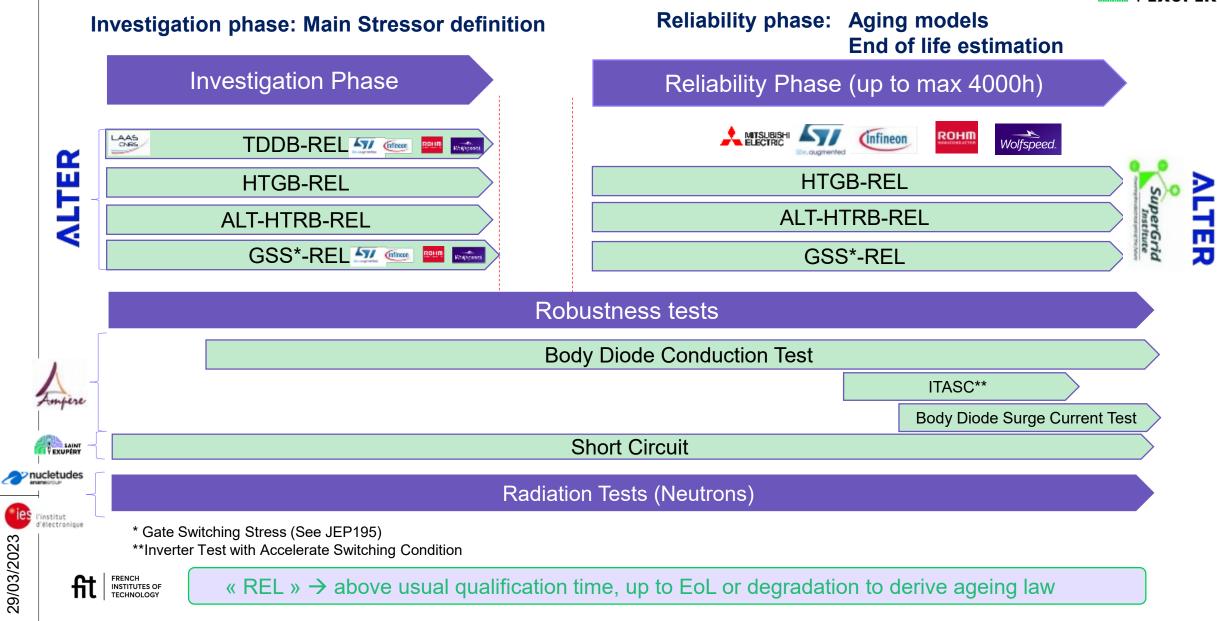

## **Reliability Methodology**

10

Optimal Approach toward costs-effective test of SiC MOSFET

© IRT Saint Exupéry • All rights reserved • Confidential and proprietary document

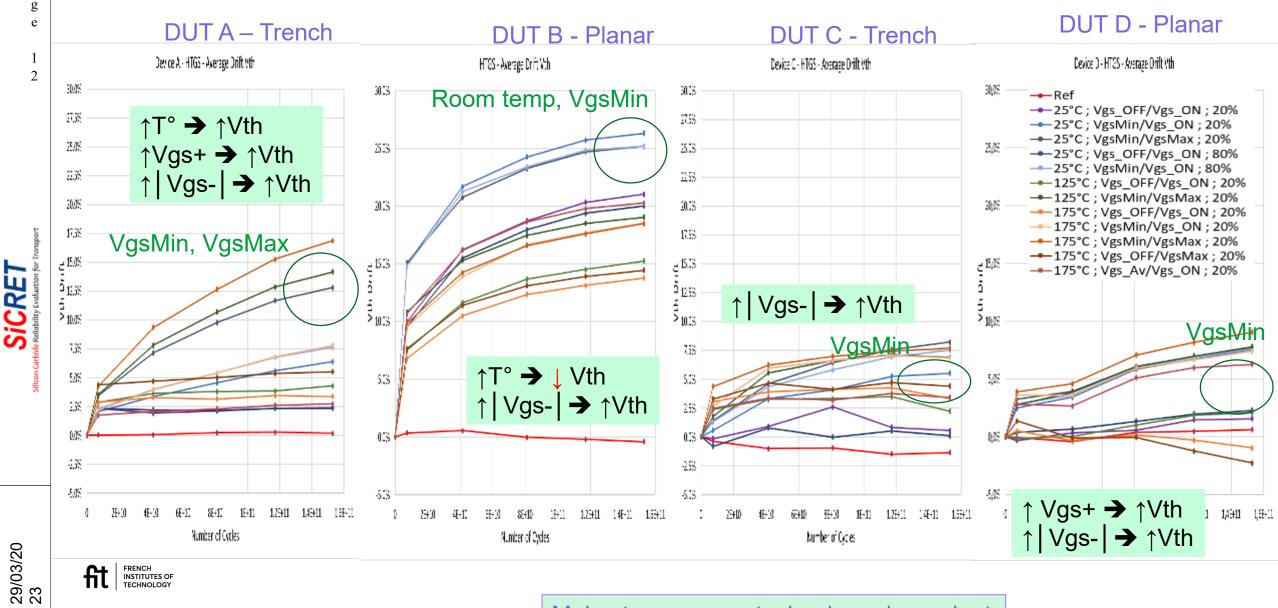

## $\textbf{HTGS} \rightarrow \textbf{GSS} \text{ test conditions} - \textbf{Screening DOE}$

Same DoE for each Manufacturer

#### **Device Selection**:

- Trench and Planar technologies

- DUT A: Trench

- DUT B: Planar

- DUT C: Trench

- DUT D: Planar

- Last SiC Mosfet generation available in 2020/2022

- TO-247-3L package

- Automotive Grade version

- Range caliber: 1200V, ~30 A, ~75 mΩ

| HTGS DoE     | Gate voltage     | Temperature | Frequency | Duty cycle | Qty |

|--------------|------------------|-------------|-----------|------------|-----|

| Condition 1  | Vgs,off / Vgs,on | 25°C        | 500 kHz   | 20%        | 3   |

| Condition 2  | VgsMin /Vgs,on   | 25°C        | 500 kHz   | 20%        | 3   |

| Condition 3  | VgsMin / VgsMax  | 25°C        | 500 kHz   | 20%        | 3   |

| Condition 4  | Vgs,off / Vgs,on | 25°C        | 500 kHz   | 80% (*)    | 3   |

| Condition 5  | VgsMin / Vgs,on  | 25°C        | 500 kHz   | 80% (*)    | 3   |

| Condition 6  | Vgs,off / Vgs,on | 125°C       | 500 kHz   | 20%        | 3   |

| Condition 7  | VgsMin / VgsMax  | 125°C       | 500 kHz   | 20%        | 3   |

| Condition 8  | Vgs,off / Vgs,on | 175°C       | 500 kHz   | 20%        | 3   |

| Condition 9  | VgsMin / Vgs,on  | 175°C       | 500 kHz   | 20%        | 3   |

| Condition 10 | VgsMin / VgsMax  | 175°C       | 500 kHz   | 20%        | 3   |

| Condition 11 | Vgs,off / VgsMax | 175°C       | 500 kHz   | 20%        | 3   |

| Condition 12 | VgsAv / Vgs,on   | 175°C       | 500 kHz   | 20%        | 3   |

#### **Glossary (from datasheet)**:

- Vgs,on: Recommended turn-on gate voltage

- Vgs,off: Recommended turn-off gate voltage

- VgMax: Max positive transient voltage

- VgMin: Min negative transient voltage

- VgsAv: Average value between VgsMin and Vgs,OFF

Investigation Test duration: 85h (1.53E+11 cycles) Remote interim Readouts: 4h, 23h, 45h, 65h

fit

**DC parameters used as indicator**: V<sub>GS(th)</sub>, R<sub>DS(ON)</sub>, VHyst, BVDSS, Vsd, Idss, Igss, Cgs, LFN, Switching Energy

р а

© IRT Saint Exupéry • All rights reserved • Confidential and proprietary document

#### Main stressors are technology dependent

## **Reliability Methodology**

13

Optimal Approach toward costs-effective test of SiC MOSFET

© IRT Saint Exupéry • All rights reserved • Confidential and proprietary document

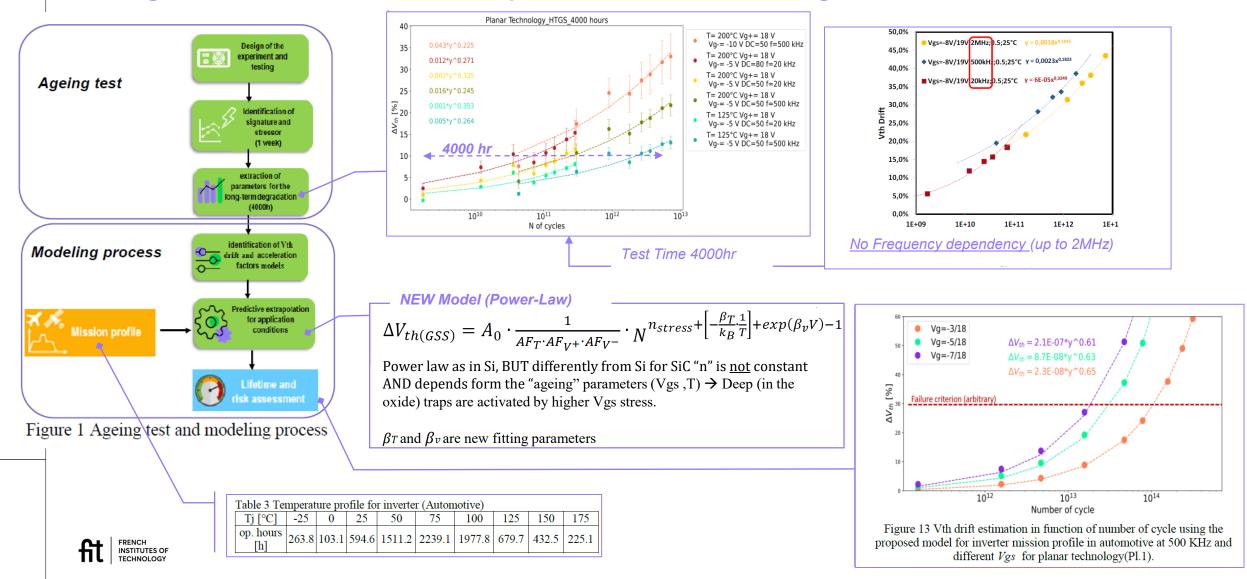

## **Reliability Model Extraction for Lifetime Prediction**

### Vth degradation model under GSS for planar and trench technologies

M. Zerarka et al., « New Reliability Model for Power SiC MOSFET Technologies Under Static and Dynamic Gate Stress » ESREF 2023 – Microelectronic Reliability 2023

## **SICRET Program: From device to Module PoF**

R SAINT

Structuring National and European SiC Industrial deployment (2019 – 2027)

Qualification Test plan Definition

User Guidelines definition (SOA, Design rules, ...)

At Power Module level including other studies/tests.

- Low pressure, humidity,

- Thermal management (power cycling, temperature cycling)

- EMC emission/immunity

- Enhanced by the collaboration with STM (associate Partner of the project)

INSTITUTES OF

Sicret

Source: ST Microelectronics

### **Lighthouse activities**

### **Connecting with Specialized Networking**

Thanks to the outcomes of the collaborative projects on reliability (SICRET/GANRET) high level scientific-technical initiatives have been engaged:

- Organization and active participation to WS on reliability of WBG devices (e.g. Expert Round tables, NRTW, ESREF...).

- Contribution to standard guidelines (e.g. AEQ324, JEDEC, AEC, ...)

- Visibility at international level: European Center for Power Electronics (ECPE); Center for Power Electronic Systems (CPES) in USA

Exchange and support international normalization bodies currently dealing with standardization of emerging WBG technologies, such as JEDEC, AEC, AFNOR, IEC...

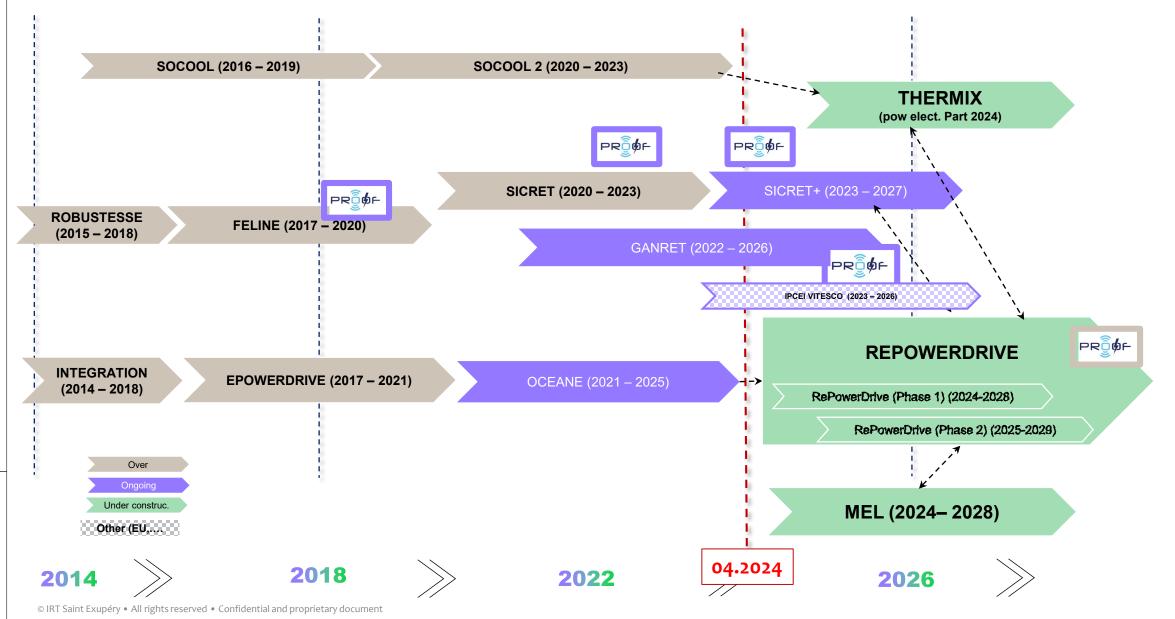

## HDRE Projects supporting roadmap (Status @ Q1-2024)

р

а

g e

22/05/2024

**Comprehensive multi-sector and multidisciplinary program: focus on Power Electronics**

### **Conclusions and Perspectives**

- ✓ PROOF is an important part of the Regional / National R&D asset and roadmap (toward electrification)

- ✓ IRT-SE consider PROOF as an essential partner to reach critical mass in WBG reliability projects

- PROOF Scientific support (expertise and equipment) instrumental in running projects (e.g. SICRET, GANRET, ...)

Much more is ongoing and has to come yet:

- Aging degradation physics modeling of WBG (beyond SiC and GaN)

- Close the gap between power electronics and HF electronics (NFS, S-Param, …

NSTITUTES OI

## Merci !

### **Acknowledgments:**

Industrial Secondments – Industrial & Institutional Experts – Accademic Advisors - IRT personnel